加油啊!企鵝們 年輕類比 FAE 的支援日誌第一話 我們該如何看待 ADC 的解析度?

初次見面。我是作為應屆畢業生加入 Macnica,目前擔任初階半導體 FAE(應用工程師)。

我原本是從一個完全不同的領域進入這家公司,因此在學習類比領域的知識時吃了不少苦頭。特別是在向客戶提案身為類比元件的 AD 轉換器 (ADC) 時,對於如何評估這些 ADC 在客戶應用中的精確度感到非常苦惱。

這一次,我想介紹一下在評估 ADC 精確度時,該如何看待與「解析度」相關的規格,這在選型時是非常關鍵的基礎。

解析度的陷阱

在挑選 ADC 時,首先關注的通常是它的精確度。當你打開規格書 (Datasheet) 時,目光可能第一眼會被封面標示的解析度數值吸引,但這裡其實藏著一個陷阱。

在我完成培訓並開始負責客戶後,曾在一次會議中收到客戶的需求,希望我推薦一款解析度在 24 位元 (bits) 以上的高精度 ADC。我向他介紹了一款 24 位元的 ADC 產品,但客戶一看到規格書,就立刻在我面前算了一下。

接著客戶回答:「這顆算是不錯,但我希望能再好一點。」

一開始我完全聽不懂他在說什麼,因為我以為規格書封面摘要的解析度就足以滿足需求了。然而,我太天真了,實際上我必須將**「有效解析度 (Effective Resolution)」和「無雜訊解析度 (Noise-Free Resolution)」**等概念考慮進去。

實際上,ADC 會產生一定程度的雜訊。這些雜訊主要由 ADC 本身固有的雜訊以及轉換過程中產生的量化雜訊組成,而這些雜訊會直接影響 ADC 實際可用的解析度。

圖 1:Analog Devices 24 位元 AD 轉換器 AD7124-4 的規格書封面

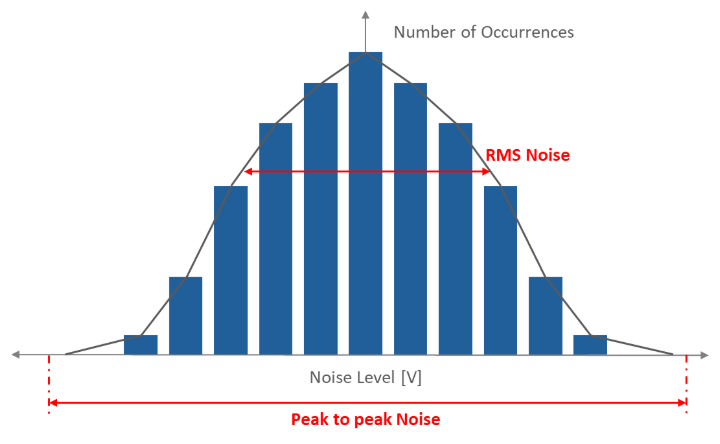

RMS 雜訊與峰對峰值雜訊

雜訊的大小機率分佈通常以高斯分佈(Gaussian Distribution)來表示。

RMS 雜訊代表高斯分佈中的標準差(有效值);而峰對峰雜訊出現的機率約佔 0.1%,通常表示為 RMS 雜訊的 6.6 倍。

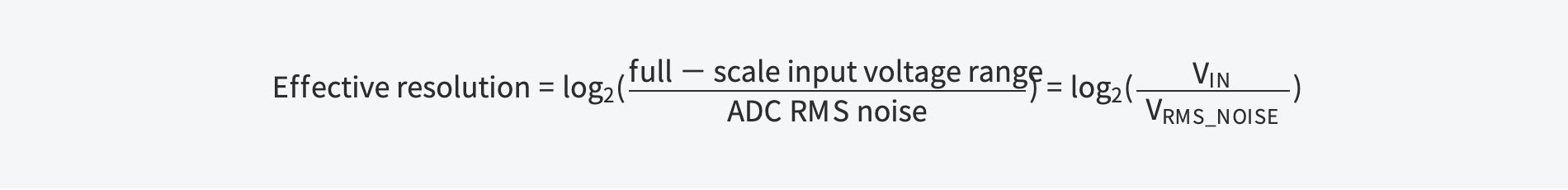

有效解析度 (Effective Resolution)

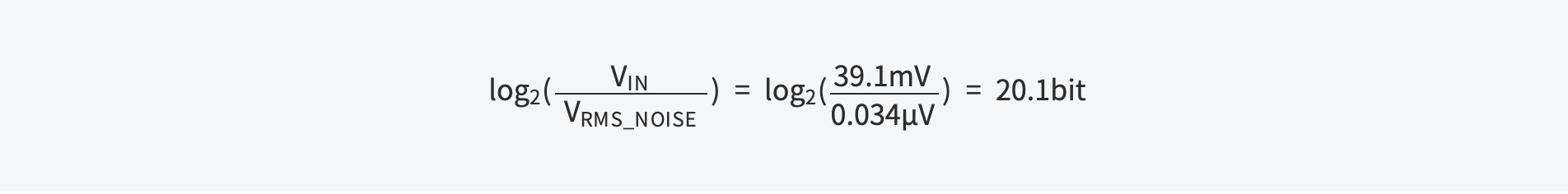

有效解析度是利用 **ADC 的 RMS 雜訊(均方根雜訊)**與 ADC 的全尺度輸入電壓(Full-scale input voltage),透過以下公式計算得出:

Effective resolution:有效解析度

-

Full-scale input voltage range:全尺度輸入電壓範圍

-

ADC RMS noise :ADC 均方根雜訊

計算實例:

以下我們以 Analog Devices (ADI) 的 **24-bit ADC「AD7124-4」**為例來計算有效解析度。ADC 的全尺度輸入電壓範圍 (Full-scale input voltage range) 是根據 參考電壓 (Reference Voltage, $V_{REF}$) 來計算的;若晶片內建了 PGA (可程式增益放大器),則必須將其 增益 (Gain) 一併納入考量。

假設在以下條件下(參考規格書圖 3):

-

使用 Sinc4 濾波器

-

取樣率 (Sampling Rate) 為 20 SPS

-

增益 (Gain) 設定為 128

-

參考電壓 ($V_{REF}$) 為 2.5 V

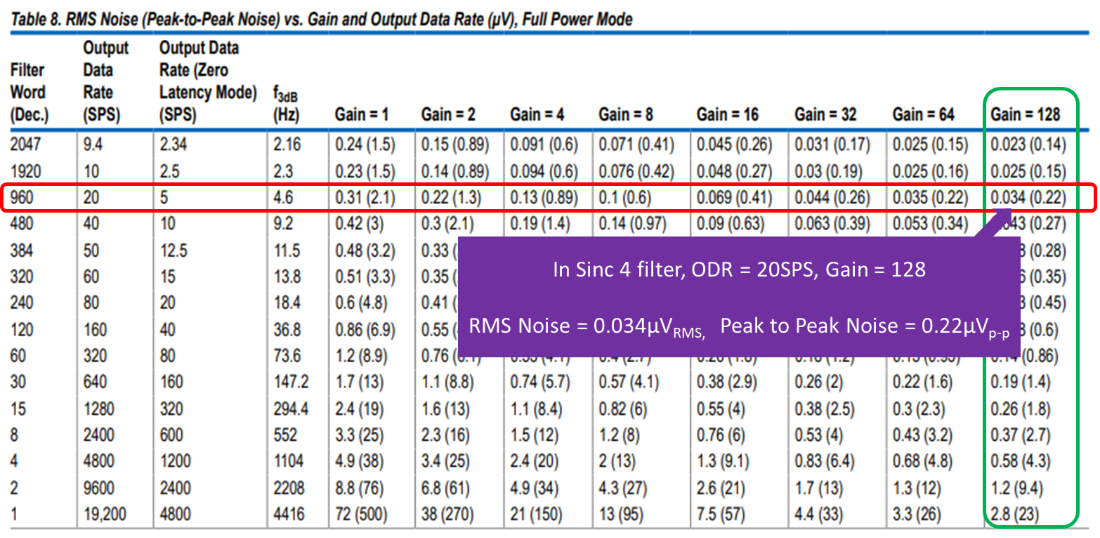

根據規格書記載,在輸入範圍為(±VREF/PGA = ±2.5V/128 = 39.1 mV).的情況下,產生的雜訊為0.034\ \mu V\ RMS。

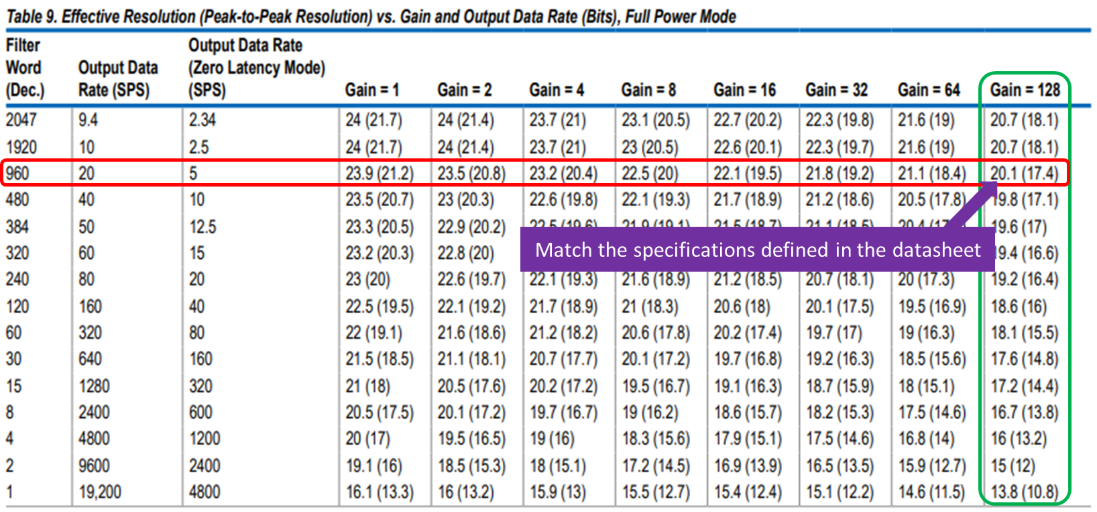

因此,有效解析度可計算如下。此外,我們也可以從規格書(參考圖 4)中確認,此計算結果與官方標示的數值是一致的:

因此,即便某款產品在上市標案中被歸類為 24-bit 產品,一旦將 RMS 雜訊納入考量並實際計算其有效解析度後,你會發現其解析度往往會低於規格書封面上所標註的 24-bit。

圖 3:AD7124-4 規格書 (Datasheet) 第 28 頁RMS 雜訊 (與峰對峰雜訊) 與增益 (Gain) 及輸出資料率 (Output Data Rate) 之對應關係表

圖 4:AD7124-4 規格書 (Datasheet) 第 28 頁

有效解析度(與無雜訊解析度)與增益 (Gain) 及輸出資料率 (Output Data Rate) 之對應關係表

在進行 ADC 選型時,最重要的就是必須釐清實際應用端 (Actual Application) 所需的真實解析度是多少。

接下來,我們將進一步探討無雜訊解析度 (Noise-free Resolution)。

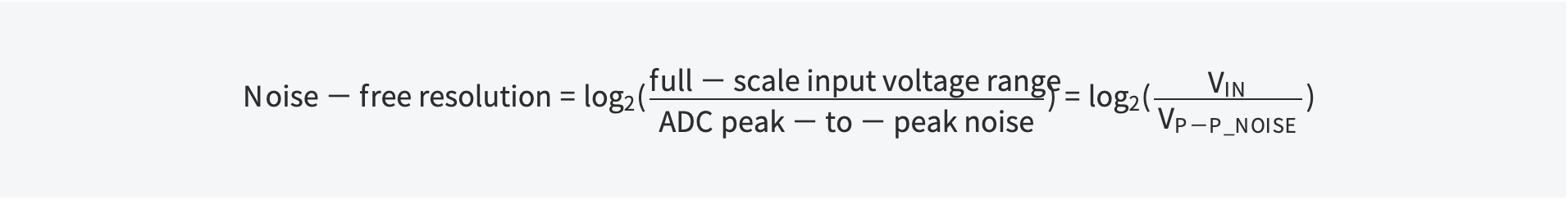

無雜訊解析度 (Noise-free Resolution)

無雜訊解析度與有效解析度的不同之處,在於計算時使用的是「峰對峰電壓雜訊 (Peak-to-Peak Voltage Noise)」而非 RMS 雜訊。無雜訊解析度同樣以 bit (位元) 為單位,定義如下:

同樣以 Analog Devices 的 24-bit ADC「AD7124-4」為例:在相同的條件下(Sinc4 濾波器、取樣率 20 SPS、增益設定 128、參考電壓 2.5 V),規格書顯示在輸入範圍 ($\pm V_{REF}/PGA = \pm 2.5V/128 = 39.1\ mV$) 內,會產生 $0.22\ \mu V_{P\text{-}P}$ 的雜訊。

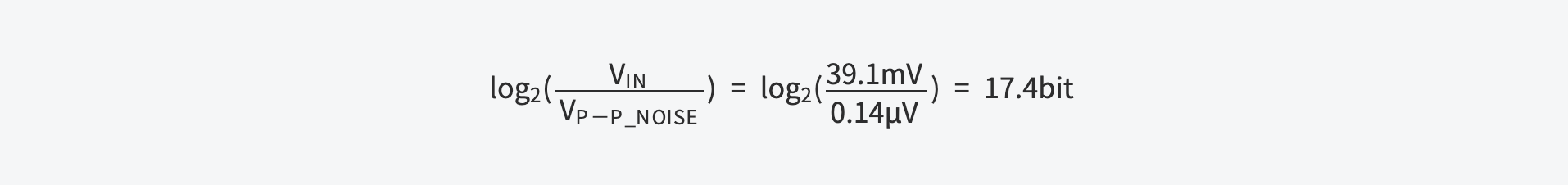

因此,無雜訊解析度計算如下(我們同樣可以從規格書圖 4 中確認計算結果與標示數值一致):

(註:原文公式中數字誤植為 0.14,依內文數據應為 0.22)

如您所見,計算出的無雜訊解析度比有效解析度少了約 2.7-bit。這是因為無雜訊解析度計入了峰對峰雜訊,根據前述的高斯分佈,峰對峰雜訊約為 RMS 雜訊的 6.6 倍,因此估算出的無雜訊解析度會低於有效解析度。

由於峰對峰雜訊會導致 ADC 輸出的 碼 (Code) 產生跳動 (Flicker),因此扣除掉這些跳動位元、更具代表性的解析度,就稱為「無雜訊解析度」。在評估 ADC 的精度時,有效解析度與無雜訊解析度這兩個概念皆至關重要。

總結

綜上所述,在評估 ADC 的解析度時,必須根據應用端 (Application) 的需求,估算出實際可用的有效位元數。

關於有效位元數有兩種思考方式:有效解析度與無雜訊解析度。由於各家供應商 (Vendor) 對於有效位元數的計算方法可能有所不同,在橫向評比不同廠牌的產品時,務必確認規格書是採用哪種方式標示。因此,在 ADC 選型時,深入理解這兩個概念對於評估元件的「真實精度」非常重要。